Mikroarchitektúra

| Ezt a szócikket át kellene olvasni, ellenőrizni a szöveg helyesírását és nyelvhelyességét, a tulajdonnevek átírását. Esetleges további megjegyzések a vitalapon. |

| Ez a szócikk nem tünteti fel a független forrásokat, amelyeket felhasználtak a készítése során. Emiatt nem tudjuk közvetlenül ellenőrizni, hogy a szócikkben szereplő állítások helytállóak-e. Segíts megbízható forrásokat találni az állításokhoz! Lásd még: A Wikipédia nem az első közlés helye. |

Az informatikában a mikroarchitektúrával teljesen leírható egy számítógép, központi egység, vagy digitális jelfeldolgozó elektromos áramkör kapcsolási sémája hardver-alapú működése. Tudományos körökben a számítógépszervezet kifejezést használják, míg a számítógépiparban a mikroarchitektúra kifejezést használják gyakrabban. Mikroarchitektúra és utasításkészlet (ISA) együtt alkotják a számítógép-architektúra területét.

A kifejezés etimológiája[szerkesztés]

Az 1950-es évek óta sok számítógép használt mikroprogramot vezérlőlogikájuk megvalósítására, ami dekódolta a programutasításokat és végrehajtotta őket. A mikroprogram kódján belüli bitek irányították a processzort az elektromos jelek szintjén. A mikroarchitektúra kifejezést arra használták, hogy leírja azokat az egységeket, amiket a mikroprogram kódjai irányítottak, szemben az architektúrával ami látható volt és dokumentált a programozóknak. Bár az architektúráknak általában kompatibilisnek kell lenniük a különböző hardvernemzedékekkel, a mögöttes mikroarchitektúrát azonban könnyen meg lehet változtathatni.

Utasításkészlet-architektúrával való kapcsolata[szerkesztés]

A mikroarchitektúra különbözik egy számítógép utasításkészletétől. Az utasításkészlet egy olyan számoló rendszernek az elvont képe, ami látható egy gépi kódot (vagy assembly nyelvet) programozó számára, beleértve az utasításkészletet, memóriacímmódokat, regisztereket, cím- és adatformátumokat. A mikroarchitektúra egy alacsonyabb szint, konkrétabban írja le a rendszert az ISA-nál. Ezen a szinten mutatkoznak meg a rendszer alkatrészei is, hogyan kapcsolódnak össze egymással, valamint miképp működnek együtt, hogy megvalósítsák az architektúra részletes leírását.

Különböző gépeknek lehet ugyanaz az utasításkészletük, ezáltal képesek ugyanazon programok futtatására, pedig különböző a mikroarchitektúrájuk. Ezek a különböző architektúrák (a félvezetőgyártás technológiájában való haladással egyetemben) azok, amik megengedik a processzorok újabb nemzedékeinek, hogy magasabb teljesítményt érjenek el az előző generációkkal összehasonlítva. Elméletben egyetlen mikroarchitektúrát (különösen ha ez mikrokódot tartalmaz) arra tudták használni, hogy megvalósítson 2 különböző utasításkészletet azáltal, hogy programoz 2 különböző vezérlő tárolót.

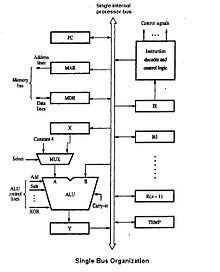

Egy gép mikroarchitektúrája általában egy olyan blokkdiagramnak tüntethető fel, ami leírja a regiszterek összekötéseit, buszokat, és a gép funkcionális blokkjait. Ez a leírás tartalmazza a végrehajtási egységek számát, a végrehajtási egység fajtáját (mint például lebegőpontos, egész szám, elágazás jövendölés, egyetlen utasítás, többszörös adatok (SIMD), a futószalag (pipeline) természete (ami tartalmazhat olyan fokozatokat, mint utasításhívás, -dekódolás, -kijelölés, -végrehajtás, -befejezés, mindezt egy nagyon egyszerű futószalagon), a gyorsítótár kialakítása (1., 2. szintű), és a perifériák támogatása.

A tényleges alapáramkör-alaprajz, hardverszerkezet, összecsomagoló, és más fizikai részleteket, a mikroarchitektúra implementációjának nevezik. Két gépnek lehet ugyanaz a mikroarchitektúrája, és ezáltal ugyanaz a blokkdiagramjuk, de különböző hardverimplementációt tartalmaznak. [4]

A mikroachitektúra aspektusai[szerkesztés]

A futószalagos adatösvény a leggyakrabban használt tervezési mód a jelenlegi mikroarchitektúrákban. Ezt a technikát a legtöbb modern mikroprocesszorban, mikrovezérlőben és DSP-ben használják. A futószalagos architektúra lehetővé teszi, hogy több utasítás átfedje egymást végrehajtás közben, kb. úgy mint egy összeszerelő szalagon. A futószalag (feldolgozási állapotok egymásutánja) több különböző állomást is magába foglal, amelyek alapvetőek a mikroarchitekturális tervezésben. Néhány állomás tartalmaz olyan műveleteket is, mint az utasításhívás, utasításdekódolás, -végrehajtás és -visszaírás. Néhány architektúra olyan állomást is tartalmaz, mint például memóriahozzáférés. A futószalagok tervezése az egyik központi mikroarchitekturális feladat.

A végrehajtási egységek is alapvetőek a mikroarchitektúrához. A végrehajtási egységek tartalmazzák az aritmetikai logikai egységeket (ALU), lebegőpontos egységeket (FPU), a töltő/tároló egységeket, az elágazás előrejelzéseket és SIMD-t. Ezek az egységek hajtják végre a műveleteket vagy a processzor kalkulációit. A végrehajtási egységek számának megválasztása, késleltetése (látenciája) és teljesítménye az egyik központi mikroachitekturális tervezési feladat. A memóriák mérete, látenciája, teljesítménye és összekapcsolhatóságuk a rendszeren belül is a mikroachitekturális döntések egyike.

A rendszerszintű tervezési döntések, mint például hogy legyenek vagy ne legyenek perifériák, értve itt memóriavezérlőket például, ugyancsak a mikroarchitekturális tervezési folyamat részének tekinthető. Ideértjük a teljesítményszintű döntéseket és ezeknek a perifériáknak az összekapcsolhatóságát.

Eltérően az architekturális tervezéstől, ahol egy bizonyos teljesítményszint elérése a fő cél, a mikroarchitekturális tervezés nagyobb figyelmet szentel az egyéb megszorításoknak. Minthogy a mikroarchitekturális tervezési döntések közvetlen befolyásolják, hogy mi kerül a rendszerbe, a következő témáknak kell figyelmet szentelni:

- csipterület / költség

- energiafogyasztás

- logikai összetettség

- kapcsolódás egyszerűsége

- gyárthatóság kérdése

- debuggolás egyszerűsége

- tesztelhetőség

Mikroarchitekturális fogalmak[szerkesztés]

Utasítás-végrehajtási ciklus[szerkesztés]

Általánosságban minden CPU, egymagos mikroprocesszor vagy többmagos megvalósítás a következő lépések végrehajtásával futtatja a programokat:

- beolvas egy utasítást és dekódolja

- megtalál minden kapcsolódó adatot, ami az utasítás végrehajtásához szükséges

- feldolgozza az utasítást

- kiírja az eredményt

Az utasításciklus folytonosan ismétlődik, amíg a tápfeszültséget ki nem kapcsolják.

A végrehajtás sebessége[szerkesztés]

Az egyszerűnek tűnő lépéssorozatot komplikálja az a tény, hogy a memóriahierarchia, amely magában foglalja a gyorsítótárat, a fő memóriát és a nemfelejtő tárolási egységeket, mint például a merevlemezeket (ahol a program utasítások és adatok vannak), mindig is lassabb volt, mint maga a processzor.

A (2) Lépés gyakran egy hosszas (CPU szempontból nézve) késést jelent, amíg az adat megérkezik a buszon keresztül. Jelentős mennyiségű kutatást fektettek olyan tervezésekbe, amelyek kikerülik ezeket a késéseket amennyire csak lehetséges. Az évek alatt az egyik központi cél az volt, hogy minél több utasítást hajtsanak végre párhuzamosan, így növelve a program effektív végrehajtásának sebességét. Ezek a törekvések bevezették a komplikált logikai és áramköri struktúrákat. Kezdetben ezeket a technikákat csak drága mainframe-eken vagy szuperkomputereken lehetett kivitelezni, köszönhetően a technikához szükséges áramkörök mennyiségének. Ahogy a félvezetőgyártás fejlődött mind több és több ilyen technika vált kivitelezhetővé az egymagos processzorokon.

- Lásd a CPU cikket a műveleti alapok részletesebb leírásához

- Lásd az általános célú CPU-k történelme cikket a CPU fejlesztések történelmének részletesebb leírásához

A következőkben azokat a mikroarchitekturális technikákat vizsgáljuk meg, amelyek közösek a mai modern CPU-kban.

Utasításkészlet-választás[szerkesztés]

Annak megválasztása hogy milyen utasításkészleti architektúrát alkalmazunk, jelentősen befolyásolja a magas teljesítményű eszközök kivitelezésének komplexitását.

Az évek alatt a számítógépmérnökök igyekeztek leegyszerűsíteni az utasításkészleteket, a tervezők inkább olyan szempontok fejlesztésére fordították az időt és energiát, amelyek a teljesítményt növelik, ahelyett hogy az utasításkészletekben rejlő komplexitásra törekedtek volna. Az utasításkészletben, tehát a hardverben realizált fejlesztések a felszínen az alkalmazások nagyobb teljesítményében jelentkeztek.

Az utasításkészletek tervezése több különböző elv szerint, a CISC, RISC, VLIW, EPIC típusokon keresztül fejlődött. Az adatok párhuzamosságával foglalkozó architektúrák tartalmazzák a SIMD-et és Vectorokat is.

Utasítás-futószalag (pipeline)[szerkesztés]

Az egyik legelső, és legerősebb technika a teljesítmény javításában az utasítás-futószalagok alkalmazása. A kezdeti processzor terveknél a fent említett összes lépés végrehajtásra került minden egyes utasításnál, mielőtt az a következő utasításra lépett volna. Az áramkörök nagy része kihasználatlanul maradt bármely egyes lépésnél, például az utasításdekódoló áramkör tétlen maradt a végrehajtási fázis közben, és így tovább.

A futószalagok növelik a teljesítményt azáltal, hogy lehetővé teszik több utasítás párhuzamos végrehajtását a processzorban.[1] Ugyanazt a fenti alappéldát nézve, a processzor elkezdené egy új utasítás dekódolását (1. lépés), míg az utolsó még az eredményre vár. Ez lehetővé teszi, hogy 4 utasítás legyen „repülés közben” ugyanabban az időben, ezáltal a processzor 4-szer olyan gyorsnak tűnik. Bár egy utasítás végrehajtása ugyanannyi időt vesz igénybe (még mindig 4 lépésből áll) a CPU egészét tekintve sokkal gyorsabban „fekteti el” az utasításokat és sokkal magasabb órajelen futtatható.

A RISC elv lerövidíti a futószalagokat, és megalkotásukat sokkal egyszerűbbé teszi azáltal, hogy egyértelműen különválasztja az utasítás eljárások egyes fázisait, azok ugyanannyi időt igényelnek – egy ciklust. A processzor egészét nézve úgy működik, mintha egy szerelőszalag lenne, az utasítások bejönnek az egyik oldalról, és az eredmények távoznak a másik oldalon. A klasszikus RISC futószalag (pipeline) csökkentett komplexitása miatt, maga a futószalag és ráadásul az utasítás-gyorsítótár is ráfér ugyanarra a méretű lapkára, amely egyébként csak magára a magra férne rá egy CISC tervezés esetében. Ez volt az igazi oka annak, hogy a RISC gyorsabb volt. A kezdeti tervezések, úgy mint a SPARC és MIPS gyakran 10× gyorsabban futottak, mint az Intel és Motorola CISC megoldásai, ugyanolyan órajelen és áron.

A futószalagok persze egyáltalában nem korlátozódnak a RISC tervezésekre. 1986-ra a csúcskategóriás VAX (a 8800-as) egy nagymértékben futószalagos kialakítás volt, időben kissé megelőzve az első kereskedelmi MIPS és SPARC kialakításokat. A legtöbb modern CPU (még a beágyazott CPU-k is) mára futószalagosak, és a futószalag nélküli mikrokódolt CPU-kat a terület korlátozottabb beágyazott processzoroknak tekintik. Nagy CISC gépek, a VAX 8800-astól a modern Pentium 4-ig és Athlonig, mind készülnek mikrokóddal és futószalagokkal. A futószalag és a gyorsítótári technikában történt fejlesztések a két legnagyobb mikroarchitekturális előrelépés, amely lehetővé tette, hogy a processzor teljesítmények lépést tartsanak az áramköri technológiákkal, amelyen alapszanak.

Gyorsítótár (cache)[szerkesztés]

Nem sok idő telt el, hogy a csipgyártásban történő fejlesztések lehetővé tették, hogy még több áramkört helyezzenek el a lapkán, és a tervezők elkezdtek utánanézni annak, miképpen lehetne ezt hasznosítani. Az egyik legkézenfekvőbb, hogy mind nagyobb mennyiségű gyorsítótár (cache) memóriát adjanak a lapkához. A gyorsítótár egyszerűen egy nagyon gyors memória, amely néhány ciklus alatt hozzáférhető a fő memória hozzáféréséhez szükséges sok-sok ciklushoz képest. A CPU tartalmaz egy gyorsítótár-vezérlőt (cache-kontrollert), amely automatizálja a gyorsítótár olvasását és írását, ha az adat már a gyorsítótárban van, akkor egyszerűen „megjelenik”, ha nem, a processzor „leállításra” kerül, amíg a gyorsítótár-vezérlő beolvassa.

RISC tervezéseknél az 1980-as évek közepétől-végétől kezdtek gyorsítótárat alkalmazni, gyakran csak 4 bájtnyit összesen. Ez a szám folyamatosan növekedett az elmúlt idő alatt, ma egy tipikus CPU kb. 512 KiB gyorsítótárral rendelkezik, míg erősebb processzorok 1–2 vagy akár 4–8 MiB-nyi gyorsítótárral is rendelkeznek, amelyeket többszintű memóriahierarchiába szerveznek. Általánosságban nézve több gyorsítótár nagyobb teljesítményt jelent.

A gyorsítótárak és futószalagok tökéletes kiegészítői egymásnak. Korábban nem volt sok értelme futószalagok építésének, amelyek gyorsabban futottak, mint a csipen kívüli memória késleltetési ideje.

A csipbe épített gyorsítótár-memória használatával a futószalag a cache memória késleltetési sebességével futhat, sokkal nagyobb sebességgel. Ez tette lehetővé, hogy a processzorok működési frekvenciája sokkal nagyobb arányban növekedjen, mint a csipen kívüli memóriáké.

Elágazásbecslés[szerkesztés]

A magasabb teljesítmény egyik gátja az utasításszintű párhuzamosságon keresztül a futószalagon belüli leállások és ürítések. Rendszerint azt, hogy egy feltételes elágazást fognak-e választani, kezdetben még nem lehet tudni, csak később a futószalagon, mivel az eseti elágazások függenek a regiszterekből származó eredményektől. Annyi idő alatt, amíg a processzor utasításdekódolója észreveszi, hogy találkozott egy feltételes elágazás-utasítással, összehasonlítva azzal az idővel, míg a regiszterből a döntő adatokat kiolvashatják, lehet, hogy a futószalagot több ciklusidőre is lefoglalják. Abból, hogy átlagban minden ötödik utasítás elágazásos utasítás, egy viszonylag hosszú felesleges eltöltött ciklusidő fakad. Ha az elágazást választják, az még rosszabb, mert a következő utasítások közül akkor mindegyiket törölni kell, amelyek már rajta voltak a futószalagon.

Az olyan technikákat, mint például az elágazásbecslés és a spekulatív végrehajtás, arra használják, hogy csökkentsék ezeket az elágazási büntetéseket. Elágazási becslés az, amikor a hardver „kitalálja”, hogy egy elágazást fognak-e választani. A találgatás várakozás nélkül engedi a hardvert előzetes utasítások végrehajtására anélkül, hogy a regisztereket olvasni kéne. A spekulatív végrehajtás egy olyan további fejlesztés, mikor a kódot a megjósolt útvonal mentén végrehajtják, mielőtt kiderülne, hogy az elágazást kell-e majd választania vagy sem.

Szuperskalár[szerkesztés]

Még a hozzáadott bonyolultság és kapuk segítségén kívül, amik szükségesek a fent említett elméletek megvalósításához, a félvezetőgyártás fejlődése engedte meg a még több logikai kapu alkalmazását.

A fent említett működés alapján a processzor egyszerre csak egy utasítást hajt végre időegység alatt. Számítógépes programokat gyorsabban tudnának végrehajtani, ha több utasítást tudnának kezelni egyidejűleg. Ez az, amit a szuperskalár processzorok valósítanak meg azáltal, hogy funkcionális egységeket, mint például az ALU-t replikálnak. A funkcionális egységek replikálása csak azután vált lehetségessé mikor egy egyszerre csak egy utasítást végrehajtó processzor gyártása már nem súrolta a megbízható gyártás határait. 1980-as évek végére a szuperskalár tervek elkezdtek belépni a piacra.

Modern tervekben általános, hogy két betöltő egységet, egy tároló egységet (sok utasításnak nincs eredménye amit tárolni kéne), kettő vagy több egész számos aritmetikai egységet, kettő vagy több lebegőpontos egységet, és gyakran egy SIMD-szerű egységet is tartalmaz. Az utasítás végrehajtó logika bonyolultsága növekszik azáltal, hogy a memóriából kiolvas egy hatalmas mennyiségű utasítást, majd átadja a megfelelő végrehajtási egységhez ami éppen tétlen. Az eredményeket aztán összegyűjtik és a végén újrarendezik.

Soron kívüli végrehajtás[szerkesztés]

A gyorsítótárak alkalmazása csökkenti a várakozások előfordulását amiatt, hogy adatokra kell várni a memóriából, de nem szabadul meg ezektől teljesen. Korai kialakításokban egy gyorsítótári hiba kényszerítené a gyorsítótár-vezérlőt, hogy állítsa le a processzort és várakozzon. Természetesen lehet abban a programban egy másik utasítás adata is, ami független az éppen végrehajtás alatt lévő utasítás eredményétől és elérhető a gyorsítótárban annál a pontnál. A soron kívüli végrehajtás megengedi annak a kész utasításnak, hogy végrehajtsák, amíg egy régebbi utasításra vár a gyorsítótárban, azután újrarendezi az eredményeket, hogy úgy tűnjön, mintha az egész programozott sorrendben történt volna.

Spekulatív végrehajtás[szerkesztés]

Egy probléma egy utasítás-futószalaggal az, hogy vannak olyan típusú utasítások, aminek teljesen végig kell haladnia a futószalagon, mielőtt a végrehajtás folytatódhat. Különösen feltételes elágazásoknak kell tudniuk egy előzetes utasítás eredményét eldönthető, hogy melyik ágat kell választani. Például, egy olyan utasításban, ami azt mondja „ha x nagyobb mint 5, akkor tedd ezt, különben tedd azt” először meg kell várni, amíg az x változó konkrét értéket kap, mielőtt eldönthető lenne, hogy ezután melyik ágon kell folytatni a végrehajtást.

Egy kisebb, négy ciklus mély futószalag esetében ez akár három ciklus késedelmet is jelenthet – a dekódolás még megtörténhet. De az órajelek növekedésével nő a futószalag nagysága, fokozatainak száma is, modern processzorokban a futószalagoknak 20 vagy több fokozata is lehet. Ebben az esetben a CPU-t minden alkalommal késleltetik a ciklusai nagy többségében, mikor ilyen utasítással találkozik.

A megoldás, vagy az egyik megoldás a spekulatív végrehajtás, ami szintén elágazásjövendölésként van nyilvántartva. A valóságban, az elágazás egyik oldala sokkal gyakrabban lesz meghívva, mint a másik, így sok esetben helyes, ha egyszerűen azt mondjuk: „x valószínűleg kisebb lesz ötnél, kezdd el annak a végrehajtását”. Ha a jóslatról kiderül, hogy helyes, hatalmas mennyiségű időt meg tudunk spórolni. A modern processzorkialakításokban már meglehetősen összetett jósló-előrejelző rendszereket alkalmaznak, amik figyelembe veszik a korábban végrehajtott elágazások eredményeit, hogy nagyobb pontossággal jósolják meg a jövőt (például: „ez a feltétel eddig már 5-ször teljesült, tegyük fel, hogy most is teljesül”).

Multiprocesszálás és többszálú működés[szerkesztés]

A számítógépek tervezőinek egyre nagyobb fejtörést okoz a CPU-k működési frekvenciái és a DRAM-ok hozzáférési idejei közötti, egyre inkább növekvő különbségek miatt. A technikák közül, amik kihasználták az utasítás-szintű párhuzamosságot egy programon belül, egyik sem bizonyult elégnek, hogy behozzák a hosszú késedelmekért elvesztegetett időt, amikor adatokat kellett elhozni a központi memóriából. Továbbá a tranzisztorok nagy száma és a magas működési frekvenciák miatt, amikre a haladóbb ILP technikák miatt volt szükség, ez nagyobb energiafelvételt igényelt, amit már nem lehetett olcsón és hatékonyan hűteni. Ezekért az okokért a számítógépek újabb nemzedékei kezdték el kihasználni a párhuzamosságnak azon a magasabb szintjeit, amik egy szimpla programon vagy programszálon kívül léteznek.

Ezt a tendenciát általában átmenő számításnak (throughput computing) szokás nevezni. Ezt az ötletet eredetileg a nagyszámítógépeknél alkalmazták, ahol az online tranzakciófeldolgozáson volt a hangsúly, beleértve az egy tranzakció végrehajtásának sebességét, valamint a hatalmas mennyiségű tranzakció kiszolgálását. Mivel a tranzakció alapú alkalmazások, mint például a hálózati útválasztás és a különböző webes szolgáltatások, az elmúlt évtizedekben rohamosan elterjedtek, a számítógépipar újra nagy hangsúlyt fektetett a kapacitás és az átmenő forgalom problémáinak kezelésére.

Ennek a párhuzamosságnak a megvalósításának egyik módja multiprocessingen keresztül, a több CPU-val rendelkező számítógépes rendszer. Csúcsminőségű szerver-számítógépek és szuperszámítógépek részére, a kisvállalkozások esetében 2–8 multiprocesszort, míg a nagy vállalatoknál, 16–256 darab multiprocesszort is használnak. Az 1990-es évek óta már megjelentek a több processzort tartalmazó PC-k is.

A félvezetők technológiájának fejlődésével a tranzisztorok méretei tovább csökkentek, ezáltal megjelentek a többmagos CPU-k, ahol több CPU-t ugyanarra a szilíciumcsipre helyeznek. Kezdetben használt csipek a beágyazott piacokat célozták meg, ahol egyszerűbb és kisebb CPU-k megengedték, hogy egy darab szilíciumlapra több processzort illesszenek. Néhány konstrukció, mint például a Sun Microsystems UltraSPARC T1, visszatért egyszerűbb (skaláris) kialakításhoz, hogy egy lapkára több processzort tudjanak illeszteni.

Egy másik technika, ami nemrég vált népszerűvé, a többszálú működés (multithreading). Ebben az esetben, mikor a processzornak a lassú rendszermemóriából kell adatokat elhoznia, akkor ahelyett, hogy várakozna az információ érkezésére, a processzor átkapcsol egy másik programba vagy a programfonálba, ami készen áll a végrehajtásra. Bár ez nem gyorsítja fel azt a program/szálat, de növeli a teljes rendszerátmenő teljesítményt azáltal, hogy csökkenti az időt, amíg a CPU tétlen.

Konceptuálisan a többszálú működés egyenértékű egy kontextuskapcsolóval az operációs rendszer szintjén. A különbség az, hogy egy többszálú CPU egy szálkapcsolást egyetlen ciklus alatt végre tud hajtani a több száz vagy több ezer ciklus helyett, amit egy kontextuskapcsoló általában igényel. Ez azáltal valósítható meg, hogy minden aktív szál számára replikálja az állapothardvert (mint például a regiszter fájl és utasításszámláló).

Egy további fejlesztés az egyidejű többszálú működés. Ez a technika szuperskalár processzoroknak, ugyanabban a ciklusban engedi végrehajtani az utasításokat különböző program/szálból egyidejűleg. Lásd az általános célú processzorok című bejegyzést más kutatási témákért, amik a processzorkialakításokkal foglalkoznak.

Jegyzetek[szerkesztés]

- ↑ Michael J. Flynn. Computer Architecture Pipelined and parallel Processor Design. Jones and Bartlett, 1–3. o. (2007)

Fordítás[szerkesztés]

- Ez a szócikk részben vagy egészben a Microarchitecture című angol Wikipédia-szócikk ezen változatának fordításán alapul. Az eredeti cikk szerkesztőit annak laptörténete sorolja fel. Ez a jelzés csupán a megfogalmazás eredetét és a szerzői jogokat jelzi, nem szolgál a cikkben szereplő információk forrásmegjelöléseként.

Források[szerkesztés]

Több blokkdiagram található itt: commons:Category:Microarchitectures

További információk[szerkesztés]

- D. Patterson and J. Hennessy. Computer Organization and Design: The Hardware/Software Interface. Morgan Kaufmann Publishers, Inc. (2004. augusztus 2.). ISBN 1-55860-604-1