VIA Nano

| VIA Nano | |

| |

| Tervező | Centaur Technology |

| Gyártó | Fujitsu, TSMC |

| FSB sebességek | 533 MHz – 1066 MHz |

| Gyártás technológia méret | 65 nm, 40 nm |

| Utasításkészlet | x86_64 |

| Architektúra | x86-64 |

| Mikroarchitektúra | VIA Isaiah |

| Magok száma | 1, 2, 4 |

| Magok nevei | Isaiah (CN) |

| L1 gyorsítótár | 64 KiB utasítás- + 64 KiB adat-gyorsítótár magonként |

| L2 gyorsítótár | 1 MiB magonként |

| Tokozás | ball grid array (felületre szerelhető) |

| Előd | VIA C7 |

A Wikimédia Commons tartalmaz VIA Nano témájú médiaállományokat. | |

A VIA Nano (korábbi kódnevén VIA Isaiah) egy személyi számítógépekbe szánt 64 bites egy- vagy többmagos mikroprocesszor. A VIA Technologies bocsátotta ki 2008-ban, öt évnyi fejlesztés után,[1] amelyet a cég CPU részlege, a Centaur Technology végzett. A 64 bites Isaiah architektúra az alapoktól kezdve teljesen új tervezés. 2008. január 24-én mutatták be[2][3][4][5] és május 29-én dobták piacra, az alacsony feszültségű változatokkal és a Nano márkanévvel együtt.[6] A processzor támogat néhány VIA-specifikus x86-os bővítményt is, amelyeket a kis fogyasztású készülékek hatékonyságának növelésére terveztek.

Történet

[szerkesztés]A VIA két különböző fejlesztési kódnevet használ minden egyes processzormagjához. Ebben az esetben, a 'CN' kódnevet az Egyesült Államokban a Centaur Technology használta. A bibliai neveket a VIA kódnevekként használja Tajvanon, és ehhez az egyedi processzorhoz és architektúrához az Isaiah (Ézsaiás) névre esett a választás. A várakozások szerint a VIA Isaiah fixpontos teljesítménye kétszerese, lebegőpontos teljesítménye négyszerese az előző generációs VIA Esther processzornak, azonos órajelen. Az elvárt energiafogyasztás is az előző generációs VIA CPU-kéval egyezett, a tervezett hőteljesítmény (TDP) 5 W és 25 W között mozog.[7] Teljesen új kialakítás lévén, az Isaiah architektúra olyan jellemzők támogatásával készült, mint az x86-64 utasításkészlet és az x86 virtualizáció, amelyek elődein, a VIA C7-es vonalon nem voltak elérhetők, miközben megtartotta a titkosítási kiterjesztéseket. Több független teszt kimutatta, hogy a VIA Nano különböző munkaterhelésekben jobb eredményeket mutat, mint az egymagos Intel Atom.[8][9][10] Az Ars Technica egyik 2008-as tesztjében egy VIA Nano jelentős teljesítményt ért el a memória-alrendszerben, miután a processzor CPUID-jét Intel-re változtatták, ami azt mutatja, hogy a benchmark szoftver a tesztkód kiválasztásához a CPU által támogatott tényleges funkciók helyett csak a CPUID-et ellenőrizte. A tesztben használt teljesítménymérő szoftver a VIA Nano megjelenése előtt készült.[11]

2009. november 3-án a VIA bemutatta a Nano 3000 sorozatot. A VIA állítása szerint ezek a modellek 20%-kal nagyobb teljesítményt és 20%-kal nagyobb energiahatékonyságot nyújtanak, mint a Nano 1000 és 2000 sorozat.[12] A VIA által végzett összehasonlító tesztek szerint egy 1,6 GHz-es 3000-es sorozatú Nano 40-54%-kal jobb teljesítményt nyújt, mint az Intel Atom N270.[13] A 3000-es sorozatban az utasításkészletet kibővítették az SSE4 SIMD kiterjesztéssel, amit az Intel Core 2 architektúra 45 nm-es kiadásában vezettek be.

2011. november 11-én a VIA kibocsátotta a VIA Nano X2 kétmagos processzort az első pico-itx alaplappal együtt. A VIA Nano X2 40 nm-es folyamattal készül és támogatja az SSE4 SIMD utasításkészlet-kiterjesztést, ami kritikus fontosságú a lebegőpontos számításokat végző alkalmazások számára.[14] A Via az állítja, hogy ennek teljesítménye 30%-kal nagyobb egy 50%-kal magasabb órajelű Intel Atom processzorénál.[15]

A VIA Nano hatalmas hátránya az, hogy nem igazi SoC, mivel nem tartalmaz grafikus chipet. Miközben az Intel az Atom újabb változatainál a grafikát teljesen a processzorba integrálta, a VIA rendszerei egy külső grafikus chipet kénytelenek alkalmazni az alaplapon, ami növeli a gyártási költségeket, és a komplexitást. Ez a technológiai hátrány a termék életciklusa során ledolgozhatatlannak bizonyult a VIA számára.

A Zhaoxin vegyesvállalat 2014-től kibocsátott processzorai a VIA Nano sorozaton alapulnak.

Jellemzők

[szerkesztés]

- x86-64 utasításkészlet

- Órajelfrekvencia 1 GHz-től 2 GHz-ig

- Buszsebesség: 533 MHz vagy 800 MHz (1066 MHz a Nano x2 esetén)

- 64 KiB adat és 64 KiB utasítás L1 gyorsítótár és 1 MiB L2 gyorsítótár magonként[16]

- 65 nm-es gyártási folyamat (40 nm a Nano x2 esetén)

- Szuperskalár sorrendtől eltérő (out-of-order) utasításvégrehajtás

- MMX, SSE, SSE2, SSE3, SSSE3 és SSE4 utasításkészlet támogatása

- x86 virtualizáció támogatása Intel-kompatibilis megvalósítással (letiltva a stepping 3 előtt)

- ECC memória támogatása

- Csatlakozó-kompatibilis a VIA C7 és VIA Eden processzorokkal

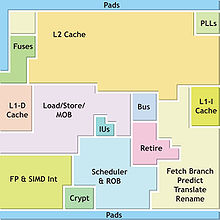

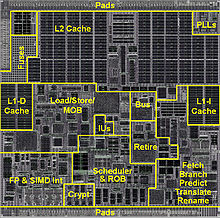

Az architektúra áttekintése

[szerkesztés]

- Sorrendtől eltérő és szuperskalár kialakítás: a VIA ebben a processzorban vezette be először ezeket a technikákat, így az Isaiah architektúrán alapuló processzorok jobb teljesítményt nyújtanak, mint elődjük, a sorrendi végrehajtású VIA C7 processzor. A VIA ezzel az architektúrával az AMD és az Intel azonos évjáratú ajánlataihoz igazodott.

- Utasításfúzió: lehetővé teszi a processzor számára, hogy több utasítást egyetlen utasításba vonjon össze; ez javítja a teljesítményt és csökkenti az energiafogyasztást. Ez a megközelítés az Atom processzorban használatos technikához (is) hasonlít,[17] ami hatékonyabb lehet, mint az utasítások kisebb egységekre bontása. Az Isaiah utasításbeolvasása az utasításokat egy kétciklusos dekódolási fázisba továbbítja, amely ciklusonként három tetszőleges méretű vagy típusú x86-os utasítást tud fogadni. A VIA állítása szerint a dekódolási fázis képes egyes x86-os utasításkombinációk, például az összehasonlítás és az ugrás Conroe-stílusú makrofúziójára, valamint a különböző kiadási portokat használó utasítások mikroutasítás-fúziójára. Az Intel Conroe-hoz (más néven Core 2 Duo) hasonlóan ez a kétféle fúzió csökkenti a menet közbeni utasítások követéséhez szükséges könyvelési logika mennyiségét.[18]

- Javított elágazás-előrejelzés: nyolc előrejelzőt (predictor) használ két futószalagfokozatban

- CPU-gyorsítótár kialakítása: kizáró (exkluzív) gyorsítótár kialakítás, ami azt jelenti, hogy az L1 gyorsítótár tartalma nem duplikálódik az L2 gyorsítótárban, így a teljes gyorsítótár-tartalom nagyobb

- Adatok előzetes lehívása (data prefetch): Az Isaiah egy speciális előzetes adatlehívó gyorsítótárral is rendelkezik, amelynek segítségével helyet takaríthat meg a normál gyorsítótár-hierarchiában. Az előretöltött adatokat jellemzően nem használják egynél többször, így nem kell foglalniuk a helyet a normál gyorsítótárban. Ez a technika az előzetesen lehívott adatokat egy speciális 64 soros gyorsítótárba helyezi, az L2 gyorsítótár és az L1-ből való közvetlen betöltés előtt.[18][19]

- négy x86 utasítást kér le utasításciklusonként, szemben az Intel három-öt ciklusával

- ciklusonként három mikroműveletet bocsát ki a végrehajtóegységek felé

- Memóriahozzáférés: a kisebb tárolókat nagyobb betöltési adatokká vonja össze

- Végrehajtó egységek: hét végrehajtó egység áll rendelkezésre, ami lehetővé teszi akár hét mikroművelet végrehajtását órajelciklusonként

- Két fixpontos (integer) egység (ALU1 és ALU2)

- Az ALU1 teljes funkcionalitású, míg az ALU2-ből hiányzik néhány ritkán használt utasítás, ezért jobban megfelel olyan feladatokra, mint a címszámítás.

- Két tárolóegység, egy a címtároláshoz és egy az adattároláshoz, a VIA szerint

- Egy betöltő egység

- Két adathordozó/média egység (MEDIA-A és MEDIA-B) 128 bit széles adatúttal, amely 4 egyszeres pontosságú vagy 2 dupla pontosságú műveletet támogat. A médiaszámítás a két adathordozó-egység használatát jelenti.

- A MEDIA-A egység végrehajtja a lebegőpontos összeadás utasításokat (2 ciklusos késleltetéssel az egyszeres és kétszeres pontossághoz), a fixpontos SIMD, titkosítás, osztás és négyzetgyökvonás utasításokat.

- A MEDIA-B egység végrehajtja a lebegőpontos szorzás utasításokat (2 ciklusos késleltetéssel az egyszeres pontosságú, 3 ciklusos késleltetéssel a kétszeres pontosságú műveletekben).

- A két médiaegységgel bevezetett párhuzamosság miatt a médiaszámítás órajelciklusonként négy összeadás és négy szorzás utasítást tud biztosítani.

- A lebegőpontos összeadás új megvalósítása, a VIA szerint az x86-os processzorok esetén legalacsonyabb órajel-latenciával.

- Majdnem minden fixpontos SIMD utasítás egy órajelen belül végrehajtódik.

- Megvalósítja az MMX, SSE, SSE2, SSE3, SSSE3 multimédiás utasításkészleteket

- Megvalósítja az SSE4.1 multimédiás utasításkészletet (VIA Nano 3000 sorozat)

- Megvalósítja az SSE4.1 multimédiás utasításkészletet (VIA Nano x2 sorozat)

- Két fixpontos (integer) egység (ALU1 és ALU2)

- Energiagazdálkodás (power management): A nagyon alacsony energiaigény mellett számos új funkciót is tartalmaz.

- Tartalmaz egy új C6 működési állapotot (gyorsítótárak törlése, belső állapot elmentve, és a mag feszültségét kikapcsolja)

- Adaptive P-State Control (adaptív P-állapot szabályozás): átmenet a teljesítmény- és feszültségi állapotok között, a végrehajtás leállítása nélkül

- Adaptive Overclocking (adaptív túlhajtás): automatikus túlhajtás, ha a processzormag hőmérséklete alacsony

- Adaptive Thermal Limit (adaptív hőmérséklethatár): a processzor beállítása a felhasználó által előre meghatározott hőmérséklet fenntartására

- Titkosítás: tartalmazza a VIA PadLock utasításkészlet-kiterjesztést (és a hozzá tartozó hardveregységet)

- Hardveres támogatás az AES titkosítás, biztonságos hash-algoritmus SHA-1, SHA-256 és véletlenszám-generálás céljaira

2014 augusztusa táján híresztelések jelentek meg egy lehetséges Isaiah II frissítésről, amely ötvözte volna a VIA által licencelt ARM technológiát az x86-os felépítéssel,[20] de a cég nem jelentetett meg ilyen terméket.

Jegyzetek

[szerkesztés]- ↑ VIA to launch new processor architecture in 1Q08. DigiTimes. [2008. december 3-i dátummal az eredetiből archiválva]. (Hozzáférés: 2007. július 25.)

- ↑ Stokes, Jon: Isaiah revealed: VIA's new low-power architecture. Ars Technica, 2008. január 23. [2008. január 27-i dátummal az eredetiből archiválva]. (Hozzáférés: 2008. január 24.)

- ↑ Bennett, Kyle: VIA's New Centaur Designed Isaiah CPU Architecture. [H]ard|OCP, 2008. január 24. [2011. július 19-i dátummal az eredetiből archiválva]. (Hozzáférés: 2008. január 24.)

- ↑ Via launches 64-bit architecture. LinuxDevices.com, 2008. január 23. [2013. január 3-i dátummal az eredetiből archiválva]. (Hozzáférés: 2008. január 24.)

- ↑ Wasson, Scott: A look at VIA's next-gen Isaiah x86 CPU architecture. The Tech Report, 2008. január 24. [2008. január 26-i dátummal az eredetiből archiválva]. (Hozzáférés: 2008. január 24.)

- ↑ VIA (29 May 2008). "VIA Launches VIA Nano Processor Family". Sajtóközlemény.

- ↑ VIA Isaiah Architecture Introduction. VIA, 2008. január 23. [2011. június 14-i dátummal az eredetiből archiválva]. (Hozzáférés: 2008. május 28.)

- ↑ Bennett, Kyle: Intel Atom vs. VIA Nano. [H]ard|OCP, 2008. július 29. [2012. február 19-i dátummal az eredetiből archiválva].

- ↑ Chiappetta, Marco: VIA Nano L2100 vs. Intel Atom 230: Head to Head. HotHardware, 2008. július 29. [2011. július 22-i dátummal az eredetiből archiválva]. (Hozzáférés: 2009. január 18.)

- ↑ Shrout, Ryan. „VIA Nano and Intel Atom Review – Battle of the Tiny CPUs”, PC Perspective, 2008. július 29.. [2010. január 13-i dátummal az eredetiből archiválva] (Hozzáférés: 2009. január 18.)

- ↑ Hruska, Joel. „Low-end grudge match: Nano vs. Atom”, Ars Technica, 2008. július 29.. [2012. január 20-i dátummal az eredetiből archiválva] (Hozzáférés: 2017. június 15.)

- ↑ VIA (3 November 2009). "VIA Introduces New VIA Nano 3000 Series Processors". Sajtóközlemény. Archiválva 2013. január 22-i dátummal a Wayback Machine-ben

- ↑ VIA Nano Processor. VIA. [2008. május 30-i dátummal az eredetiből archiválva]. (Hozzáférés: 2008. május 30.)

- ↑ VIA Releases New Nano X2 Dual-Core Processor. Tom's Hardware. [2022. január 25-i dátummal az eredetiből archiválva]. (Hozzáférés: 2013. október 15.)

- ↑ VIA Nano x2 Processor SPECfp2000 Benchmarks. VIA. [2014. február 7-i dátummal az eredetiből archiválva].

- ↑ The VIA Isaiah Architecture - VIA Technologies, Inc., 2013. május 29. [2013. május 29-i dátummal az eredetiből archiválva]. (Hozzáférés: 2020. április 10.)

- ↑ Anand Lal Shimpi: Intel's Atom Architecture: The Journey Begins / Return of the CISC: Macro-op Execution (angol nyelven). CPUs. AnandTech, 2008. április 2. (Hozzáférés: 2024. április 1.)

- ↑ a b Jon Stokes: Isaiah revealed: VIA’s new low-power architecture (angol nyelven). Tech. Ars Technica, 2008. január 24. (Hozzáférés: 2024. április 1.) „Conroe-style macro-fusion ... and micro-ops fusion”

- ↑ Stokes 2008 Data flow and cache hierarchy

- ↑ VIA's new Isaiah x86/ARM hybrid CPU outperforms Intel in benchmarks. ExtremeTech. [2014. november 12-i dátummal az eredetiből archiválva]. (Hozzáférés: 2014. november 16.)

Fordítás

[szerkesztés]Ez a szócikk részben vagy egészben a VIA Nano című angol Wikipédia-szócikk ezen változatának fordításán alapul. Az eredeti cikk szerkesztőit annak laptörténete sorolja fel. Ez a jelzés csupán a megfogalmazás eredetét és a szerzői jogokat jelzi, nem szolgál a cikkben szereplő információk forrásmegjelöléseként.

Források

[szerkesztés]- ↑ Stokes 2008: Stokes, Jon: Isaiah revealed: VIA’s new low-power architecture (angol nyelven). Tech. Ars Technica, 2008. január 24. (Hozzáférés: 2024. április 1.)

További információk

[szerkesztés]- VIA Nano Processor Archiválva 2008. május 30-i dátummal a Wayback Machine-ben.

- VIA Nano X2 Dual-Core Processor Archiválva 2011. január 9-i dátummal a Wayback Machine-ben

- VIA QuadCore Processor Archiválva 2014. június 25-i dátummal a Wayback Machine-ben

Sajtó

[szerkesztés]- The Battle of Low-Power Processors: Best Choice for a Nettop, 2008. szeptember 27. [2013. október 25-i dátummal az eredetiből archiválva].

- Low-end grudge match: Nano vs. Atom, 2008. július 30.

- Via's Nano L2100 takes on Intel's Atom 230, 2008. július 30.

- janpotocki: Nano néven debütált a VIA új processzorgenerációja (magyar nyelven). Processzor. Prohardver, 2008. május 29. (Hozzáférés: 2024. március 31.)