hyperSPARC

| hyperSPARC | |

| Gyártás | 1993 – 1996 |

| Tervező | Ross Technology |

| Gyártó | Fujitsu, NEC |

| Max CPU órajel | 40 – 200 MHz |

| Gyártás technológia méret | 0,65 µm, 0,35 µm |

| Architektúra | SPARC V8 |

| Magok száma | 1, 2 egy MCM modulban |

| L1 gyorsítótár | 8 KiB utasítás |

| L2 gyorsítótár | 256, 512, 1024 KiB |

| Tokozás | MCM, 131 lábú PGA |

| Foglalat | processzorkártyán |

A Wikimédia Commons tartalmaz hyperSPARC témájú médiaállományokat. | |

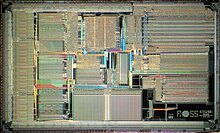

A hyperSPARC, kódnevén „Pinnacle”, egy az SPARC Version 8 utasításkészlet-architektúrát (ISA) megvalósító mikroprocesszor, amelyet a Ross Technology fejlesztett a Cypress Semiconductor cég számára. A SPARC Version 8 specifikáció szerint tehát ez egy 32 bites, big-endian bájtsorrendű processzor, egyszeres, kétszeres és négyszeres pontosságú lebegőpontos aritmetikával.

A hyperSPARC processzort 1993-ban mutatták be, és a Sun SuperSPARC processzoraival versengett. A hyperSPARC mikroarchitektúráját Raju Vegesna tervezte, ennek első szimulátoros verzióját pedig Jim Monaco készítette.[1] Tervezésekor célul tűzték ki a teljes SPARC kompatibilitást (SPARC V8 architektúra, az MMU és a 2. szintű MBus kompatibilitással együtt), a CMOS technológiát, az azonos kiszerelést, valamint a SPARC processzoroknál 3–5-ször gyorsabb működést.[2]

A hyperSPARC volt a Sun Microsystems első számú riválisa az 1990-es évek közepén. Mikor a Fujitsu megszerezte a Ross Technology-t a Cypress-től, az elemzők szerint az új tulajdonos a hyperSPARC kialakítást sokkal fontosabbnak tartotta, mint a HAL Computer Systems – szintén a Fujitsu leányvállalata – által fejlesztett SPARC64 tervezetet, amely 64 bites, SPARC Version 9 specifikációnak megfelelő processzor, és 1995-ben készült el.

Leírás

[szerkesztés]

A hyperSPARC processzort egy szorosan csatolt csipkészlet formájában valósították meg, amely többlapkás (multi-die packaging, MDP) tokozásban, szabványos SPARC MBus modulként készült. A hyperSPARC CPU 256, 512 vagy 1024 KiB második szintű gyorsítótárat támogat, és minden modul 1 vagy 2 CPU-t tartalmazhat. A csipkészlet elemei az RT620 központi egység, az RT625 vagy RT626 gyorsítótár-vezérlő, memória- és „tag”-kezelő egység (CMTU), és négy RT627 gyorsítótár-adategység (CDU) 256 KiB második szintű gyorsítótár, négy RT628 CDU 512 KiB második szintű gyorsítótár, vagy nyolc RT628 CDU 1 Mbyte második szintű gyorsítótár esetén. A csipkészlet konfigurálható egyprocesszoros működésre 1. szintű MBus mellett, vagy multiprocesszoros működésre, ekkor 2. szintű MBus-t alkalmaz.[2]

A hyperSPARC központi egysége egy kétutas szuperskalár mikroprocesszor. Négy végrehajtóegysége van: egy fixpontos egység, egy lebegőpontos egység, egy betöltő-tároló egység és egy elágazáskezelő egység. A hyperSPARC-nak egy lapkára integrált 8 KiB-os utasítás-gyorsítótára van, amiből a rendszer két utasítást hív le és dekódol ciklusonként. A dekóder nem képes dekódolni az újabb utasításokat, ha a kibocsátási puffere betelt, azaz ha már dekódolt utasítások várakoznak kibocsátásra a végrehajtó egységekhez.

Az egész-aritmetika számára rendelkezésre álló regisztertár 136 regisztert tartalmaz, amelyek felett nyolc globális regisztert és nyolc 24 regiszteres egymást átfedő regiszterablakot biztosít – ez a SPARC ISA (utasításkészlet-architektúra) által meghatározott szokásos tulajdonság. A regisztertárnak két olvasási kapuja van. A fixpontos egység egy négy fokozatú utasítás-futószalaggal rendelkezik, amelyben két fokozat csak amiatt szerepel, hogy a futószalag hossza megegyezzen a többi nemlebegőpontos futószalagéval – a betöltő-kiíró (load/store) és elágazási futószalagokkal. A futószalagok négy fokozata a szokásos: végrehajtás, gyorsítótár-olvasás, gyorsítótár-írás, és regisztertár frissítés. A fixpontos számítóegység nem használja ki a gyorsítótár-fokozatokat, de azok ennél is megvannak, a fokozatok szinkronizációja miatt. A SPARC architektúra V8-as verziójában megjelent egész típusú szorzás- és osztás-utasítások a hyperSPARC processzornál viszonylag hosszúak: a szorzás 18, az osztás 37 ciklusos várakoztatással hajtódik végre, azaz ennyi ciklus idejére megállítja az utasításfeldolgozó futószalagot és blokkolja az új utasítások kibocsátását.[1]

A processzor támogatja multiprocesszálást a SPARC MBus sínrendszerű gépekben.

Fizikai jellemzők

[szerkesztés]A hyperSPARC 1,2 millió tranzisztorból áll. A Cypress gyártotta saját 0,65 µm-es, két fémrétegű CMOS folyamatával. A hyperSPARC későbbi modelljeinek több tranzisztora volt, a bevezetett új tulajdonságok miatt, és ezeket alkalmassá tették újabb folyamatokkal történő gyártáshoz is. Az 1997-ben bemutatott 200 MHz-es hyperSPARC processzor a Fujitsu 0,35 µm-os három fémrétegű (TLM) CMOS technológiájával készült.[3] A processzorokat a Fujitsu gyártotta, kivéve az utolsó sorozatot, amit a NEC Corporation.

Tokozás

[szerkesztés]A hyperSPARC többcsipes felépítésű. Kerámia tokos többcsipes modulként (multi-chip module, MCM)[4] készült, 131 lábú pin grid array (PGA) csatlakozással.[5] Maguk a processzorok standard MBus processzorkártyákra szerelve kerültek forgalomba.

Csipkészlet

[szerkesztés]A hyperSPARC a Cypress SparcSet csipkészletet használta, amit 1992 július végén mutattak be. Ezt a kaliforniai Santa Clara-beli Nimbus Technologies, Inc. start-up cég fejlesztette a Cypress-nek, amely a kialakítást gyártotta. A SparcSet más SPARC mikroprocesszorokkal is kompatibilis.

Modellek

[szerkesztés]A táblázat a különböző megjelent változatok fontosabb adatait mutatja.

| Ross/Bridgepoint SPARC mikroprocesszorok | |||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Modell | órajel [MHz] |

architektúra verzió |

év | gyártás [µm] |

tranzisztorok [millió] |

mag méret [mm²] |

IO pinek | fogyasztás [W] |

feszültség [V] |

L1 adat gy.tár[6] (Dcache) [KiB] |

L1 utasítás- gy.tár (Icache) [KiB] |

L2 gy.tár [KiB] |

L3 gy.tár [KiB] |

| HyperSPARC A | 55–80 | V8 | 1993 | 0,5 | 1,5 | – | – | – | 5 | nincs | 8 | 256 | nincs |

| HyperSPARC B | 90–125 | V8 | 1995 | 0,4 | 1,5 | – | – | 25 | 5 | nincs | 8 | 256 | nincs |

| HyperSPARC C | 110–166 | V8 | 1995 | 0,35 | 1,5 | – | – | 45,5 | 5 | nincs | 8 | 1024 | nincs |

| HyperSPARC D | 180–200 | V8 | 1995 | 0,35 | 1,7 | – | – | – | 5 | 16 | 16 | 1024 | nincs |

Jegyzetek

[szerkesztés]- ↑ a b John Paul Shen, Mikko H. Lipasti. 8.3.14.2 Ross HyperSPARC (Pinnacle) / 1993., Modern Processor Design (angol nyelven). Long Grove, IL: Waveland Press, Inc., 434. o.. isbn 1-4786-0783-1, 978-1-4786-0783-0 [2005] (2013) „A preliminary article on the HyperSPARC was published by Vegesna [1992].”

- ↑ a b hyperSPARC: whitepaper (angol nyelven) (pdf) pp. 1/11. Ross Technology, 1995. március 1. [2015. április 2-i dátummal az eredetiből archiválva]. (Hozzáférés: 2016. október 29.)

- ↑ ROSS Technology: ROSS Announces Quad 200 MHz/512K hyperSPARC(TM) Upgrades (angol nyelven) (txt). PR Newswire, 1997. június 9. [2015. április 2-i dátummal az eredetiből archiválva]. (Hozzáférés: 2016. október 29.)

- ↑ A Ross Technology terminológiájában: multi-die packaging, MDP

- ↑ MDP Improves Microprocessor Design (angol nyelven) (pdf) pp. 1. ROSS Technology, Inc., 1996. „... conflicting goals can be met by utilizing multi-die packaging (MDP) technology as ROSS has demonstrated recently with their 90 MHz hyperSPARC.”

- ↑ gyorsítótár, cache

Fordítás

[szerkesztés]Ez a szócikk részben vagy egészben a hyperSPARC című angol Wikipédia-szócikk ezen változatának fordításán alapul. Az eredeti cikk szerkesztőit annak laptörténete sorolja fel. Ez a jelzés csupán a megfogalmazás eredetét és a szerzői jogokat jelzi, nem szolgál a cikkben szereplő információk forrásmegjelöléseként.

Források

[szerkesztés]- Levine, Bernard (11 April 1994). "MCM advocates lure would-be users". Electronic News.

- Holden, Daniel (15 February 1993). "Cypress, Sun: HyperSPARC hypertension". Electronic News.

- Holden, Daniel (15 March 1993). "HyperSparc eyes union with Intel on P6 processor". Electronic News.

- Holden, Daniel (19 April 1993). "HyperSPARC slow going with Sun Micro". Electronic News.

- Shen, John Paul and Lipasti, Mikko H. (2004). Modern Processor Design. McGraw-Hill Professional.

További információk

[szerkesztés]- "Ross Previews Pinnacle SPARC Design". (25 March 1992). Microprocessor Report, vol. 6, no. 4.

- "TI and Cypress/Ross Battle for SPARC Leadership". (27 May 1992). Microprocessor Report, vol. 6, no. 7.

- "Ross Finally Ships HyperSPARC". (15 November 1993). Microprocessor Report, vol. 7, no. 15.

- "Enhanced HyperSparc Challenges UltraSparc". (4 December 1995). Microprocessor Report, vol. 9, no. 16.

- Raju Vegesna, MD and CEO, Sify Technologies (angol nyelven). tele.net.in, 2011. március 25. [2013. július 10-i dátummal az eredetiből archiválva]. (Hozzáférés: 2016. október 29.) – Raju Vegesna indiai számítógéptervező