Flipflop (elektronika)

A digitális hálózati elemek közül flipflopnak (bistabil multivibrátor) nevezik azokat, amelyek egyidejűleg tudják fogadni a következő bemenetet, és szolgáltatni az aktuális kimenetet, így egyszerű memóriaelemként is használhatóak. Vezérelhetőek több órajellel, egy órajel felfutó és lefutó élével, vagy logikai kapukkal. Előnyös tulajdonságuk, hogy két állapot közötti átmenetkor nem válnak átlátszóvá. Gyakran a kimeneteik negáltját is szolgáltatják.

Fajtái[szerkesztés]

A flipflopoknak több fajtája létezik, így beszélhetünk:

- SR (Set-Reset) flipflopról

- D (Data) flipflopról

- DG (Data-Gate) flipflopról

- T (toggle) flipflopról

- JK flipflopról

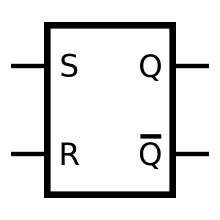

Az S-R flipflop[szerkesztés]

Az S-R flipflopnak egy beállító (Set), és egy törlő (Reset) bemenete van. Az egyik legegyszerűbb flipflopnak tekinthető, bár alapvetően tároló. A két bemenet egyidejű felemelését tiltani szokták, mivel ez instabil állapotot idézne elő (ld. versenyhelyzet), viszont ha egy D flipfloppal kombináljuk, és mindkét bemenet egyidejű felemelését engedélyezzük, akkor master-slave JK flipflopot kapunk.

Igazságtáblája:

| S | R | Qkövetkező |

| 0 | 0 | Q |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | X |

(X = Tiltott kimenet)

A D flipflop[szerkesztés]

A D flipflop a legegyszerűbb, 1 bites memóriaelemnek tekinthető. Létezik élvezérelt, és két fázisú órajellel vezérelt típusa is. Alapvetően két D-G tárolóból áll, amelyek master-slave elrendezésűek, tehát az első által fogadott jelet a második – vezérléstől függően – a következő fázisban másolja a kimenetre.

Igazságtáblája:

| D | Qn+1 |

| 0 | 0 |

| 1 | 1 |

A D-G flipflop[szerkesztés]

A DG (Data-Gate) flipflop G bemenete reteszként működik (ezért nevezik Latch-nek is). Ha tehát ez a magas szintű, akkor a D a kimenetre kerül (másol). G = 0 esetén a kimenetet megőrzi, vagyis ilyenkor D nem befolyásolja az értékét.

Igazságtáblája:

| D | G | Qn+1 |

| 0 | 0 | Qn |

| 0 | 1 | 0 |

| 1 | 0 | Qn |

| 1 | 1 | 1 |

A T flipflop[szerkesztés]

A T flipflop magas szintű bemenet esetén a kimenetét negálja.

Igazságtáblája:

| T | Qn+1 |

| 0 | Q |

| 1 | !Q |

A JK flipflop[szerkesztés]

Ha egy SR tároló mindkét bemenetének magas szintűre állítása esetén azt szeretnénk, hogy a kimenetet negálja, akkor – az instabil állapotok kiküszöbölése céljából – egy D flipflopot teszünk a JK tárolónkra. Az ábrán látható JK flipflopon egy beállító és egy törlő bemenet is van, ezeket a kezdeti állapotuk beállítására lehet használni. (Általában nem Set és Reset szoktak lenni, hanem Preset és Clear.)

Igazságtáblája:

| J | K | Qkövetkező |

| 0 | 0 | Q |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | !Q |

| Q | Qkövetkező | J | K |

| 0 | 0 | 0 | X |

| 0 | 1 | 1 | X |

| 1 | 0 | X | 1 |

| 1 | 1 | X | 0 |

Preset és Clear[szerkesztés]

A flipflopokon szoktak elhelyezni preset és clear (set és reset) bemeneteket a kezdeti beállítás céljából. Ha nincs rajta, akkor egyszerűen szerkeszthetőek, az alábbi igazságtáblák szerint:

Preset:

| Jel | Preset | Kimenet |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Kimenet = Preset + Jel (+ = logikai vagy)

Clear:

| Jel | Clear | Kimenet |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Kimenet = !Clear * Jel (* = logikai és)

További információk[szerkesztés]

DHLAB letöltése[halott link] – digitális hálózat tervező program